Applications

AI Data Center Scale Up

Avicena’s microLED interconnects are ideal for Scale Up applications, which require high shoreline density (> 1 Tbps/mm), ultra-low power (< 1 pJ/bit) connections with reaches up to 20 meters. This positions Avicena in the sweet spot between short reach copper (1 meter or less) and long reach optical interconnects (> 20 meters).

Copper dominates Scale Up today because it’s low cost, reliable and energy efficient. However, copper’s limited reach makes it impractical to scale beyond a few dozen GPUs. Standard optical technologies such as lasers and active optical cables are well suited to the longer connections between racks for Scale Out, but they’re too complex, power hungry and costly for Scale Up.

Unlike alternative approaches, Avicena’s µLED interconnects enable GPU clusters to Scale Up across multiple racks, linking thousands of GPUs, while achieving industry-leading sub-pJ/bit energy efficiency.

Optical Memory Interconnects

Optical Memory Interconnects address the unique challenge of moving data between processors and memory with low latency and high bandwidth. Like Scale Up, this requires high density bandwidth, ultra-low power, and short reach connections, as well as new techniques such as memory disaggregation. microLED interconnects are particularly well suited for memory disaggregation because the “wide & slow" architecture has 100s to 1,000s of lanes each running at data rates of a few Gbps.

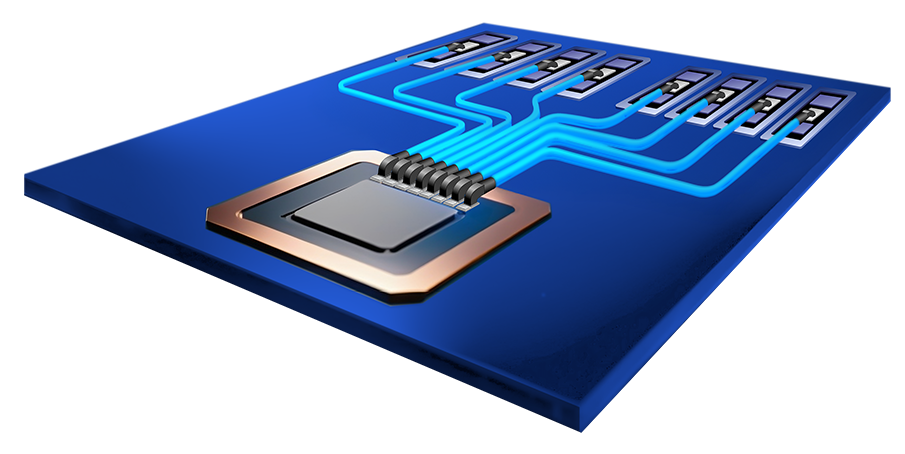

For example, one of the bottlenecks in processor to memory interactions is the physical layout and placement of memory chips around the microprocessor, which effectively limits total capacity. Memory disaggregation addresses this challenge by moving the High-Bandwidth Memory (HBM) away from the microprocessor, enabling larger memory banks. Avicena’s µLED interconnects with co-packaged optics provide high bandwidth connections between the microprocessor and memory banks.