Applications

Avicena LightBundle™ microLED interconnect technology is purpose-built for scale-in and scale-up Al infrastructure requiring extreme bandwidth density, ultra-low energy per bit, and high-reliability connectivity.

By eliminating the reach and routing constraints of copper and the reliability, power, and cost challenges of laser-based optics. LightBundle enables scalable interconnects between XPUs, switches, and NICs within racks, as well as connectivity innovation breakthroughs between XPUs and memory.

These capabilities unlock advanced chip-to-chip and chip-to-memory architectures that overcome memory-wall limitations and maximize data-center-level performance.

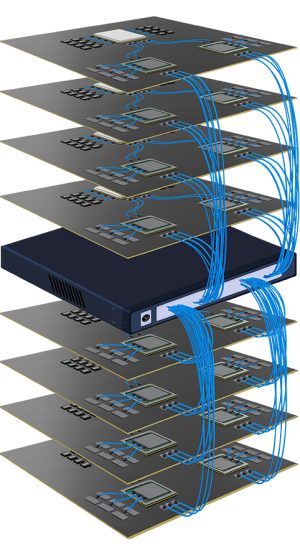

Scale-Up

Within same rack

XPU <-> XPU and XPU <->Switch

Reach: from 1 meter to > 20 meter

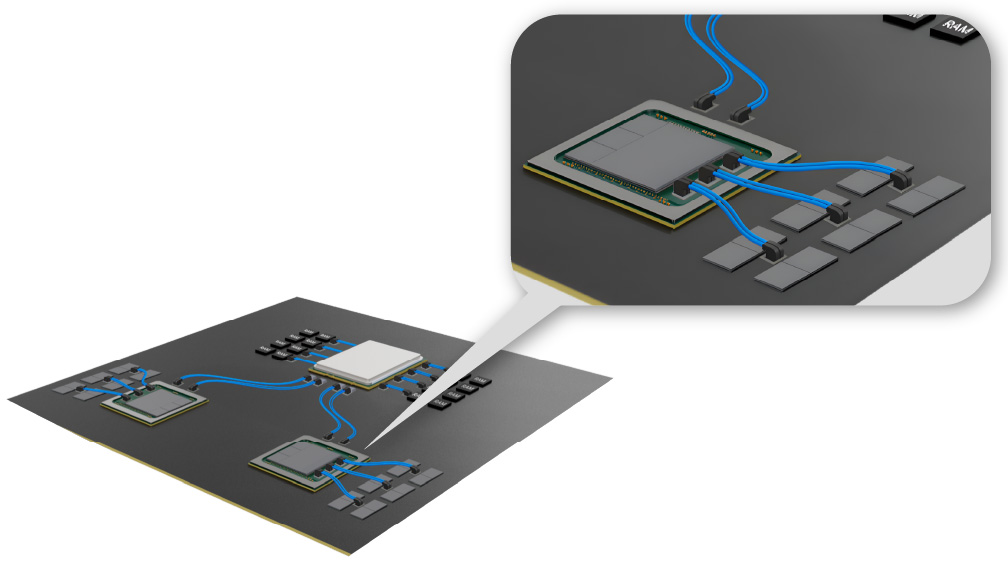

Scale-In

Die-to-die

XPU <-> XPU and XPU <-> HBM

Reach: from few mm to 1 meter